# Acquisition d'images Zynq

**Simon DOPPLER**

Travail de Bachelor 2019

INF – IIE

Professeur-e-s : Yves MEYER

Expert-e-s : Yves CESTELE

## Description

Swiss Timing LTD réalise les chronométrages de compétitions sportives pour le compte des entreprises du Swatch Group. Afin de pouvoir départager les concurrents de courses qui arrivent très proches l'un de l'autre, la ligne d'arrivée est photographiée sous la forme d'une ligne unique de pixels, qui permettent de lire le temps auquel le concurrent a passé la ligne.

Avec la technologie des capteurs d'images numériques, il n'est pas possible de prendre toutes les couleurs sur chaque pixel mais uniquement une couleur (rouge, vert ou bleu) par pixel. Il faut donc utiliser un algorithme dit de *deBayering* qui calcule les couleurs manquantes.

Afin de réaliser cette opération rapidement et ainsi obtenir une précision de mesure plus grande, il a été décidé de l'implémenter sous forme de circuit logique numérique spécialisé.

## Résultats

L'implémentation de l'algorithme de *deBayering* est fonctionnelle : elle fonctionne dans la plage de vitesse d'acquisition demandée (8300 images/seconde avec la caméra) et elle respecte les couleurs de la caméra, l'image en sortie de la caméra a un histogramme plat, qui reste plat à travers le système implémenté dans ce travail de bachelor.

Cependant, le passage de l'image de la partie logique (implémentée dans ce travail) à l'ordinateur n'est pas suffisamment rapide pour être utilisable.

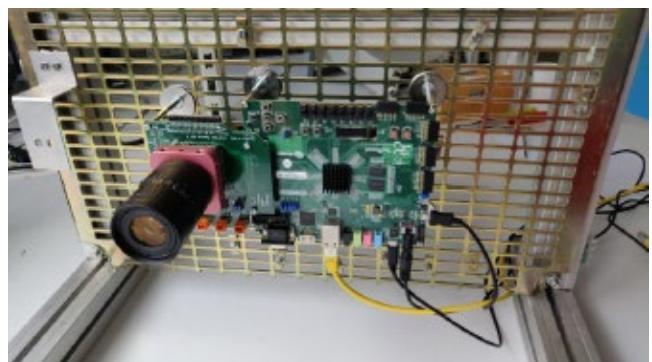

Système assemblé

## Déroulement

- Analyse du cahier des charges et planification du projet

- Étude du fonctionnement de la caméra et de la carte d'adaptation réalisée dans un travail de bachelor précédent.

- Implémentation du contrôle de la caméra

- Étude des bus de transport de l'information dans la carte d'acquisition

- Étude de l'algorithme de *deBayering* et implémentation de cet algorithme en VHDL dans la carte Zynq

- Validation du résultat du travail

## Perspectives

Dans la suite de ce travail de bachelor, il serait possible de d'implémenter l'ensemble du système sous forme de circuit logique, afin de le rendre plus rapide et ainsi permettre de respecter les vitesses requises avec l'ensemble du travail.